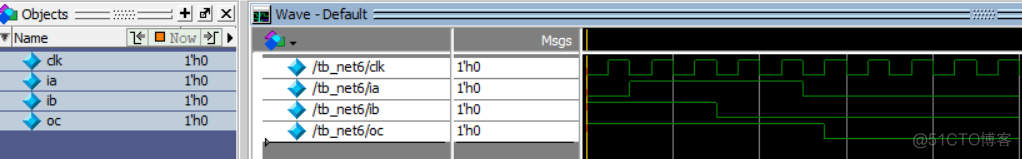

// This is a simple example. // You can make a your own header file and set its path to settings. // (Preferences > Package Settings > Verilog Gadget > Settings - User) // // "header": "Packages/Verilog Gadget/template/verilog_header.v" // // ----------------------------------------------------------------------------- // Copyright (c) 2014-2021 All rights reserved // ----------------------------------------------------------------------------- // Author : lingaitao 791347720@ // File : net6.v // Create : 2021-07-20 22:22:25 // Revise : 2021-07-20 22:22:25 // Editor : sublime text3, tab size (4) // ----------------------------------------------------------------------------- module net6( input wire ia, input wire ib, input wire clk, output reg oc=1 ); always@(posedge clk) begin oc<=ia |ib; end endmodule

// This is a simple example. // You can make a your own header file and set its path to settings. // (Preferences > Package Settings > Verilog Gadget > Settings - User) // // "header": "Packages/Verilog Gadget/template/verilog_header.v" // // ----------------------------------------------------------------------------- // Copyright (c) 2014-2021 All rights reserved // ----------------------------------------------------------------------------- // Author : yongchan jeon (Kris) poucotm@ // File : tb_net6.v // Create : 2021-07-20 22:28:17 // Revise : 2021-07-20 22:36:09 // Editor : sublime text3, tab size (4) // ----------------------------------------------------------------------------- `timescale 1ns/1ns module tb_net6(); reg clk; reg ia,ib; wire oc; initial begin ia=0; ib=1; clk=0; #10 ia=1; #20 ib=0; #20 ia=0; end always #5 clk=~clk; net6 tb_net6_inst( .ia (ia), .ib (ib), .clk (clk), .oc (oc) ); endmodule

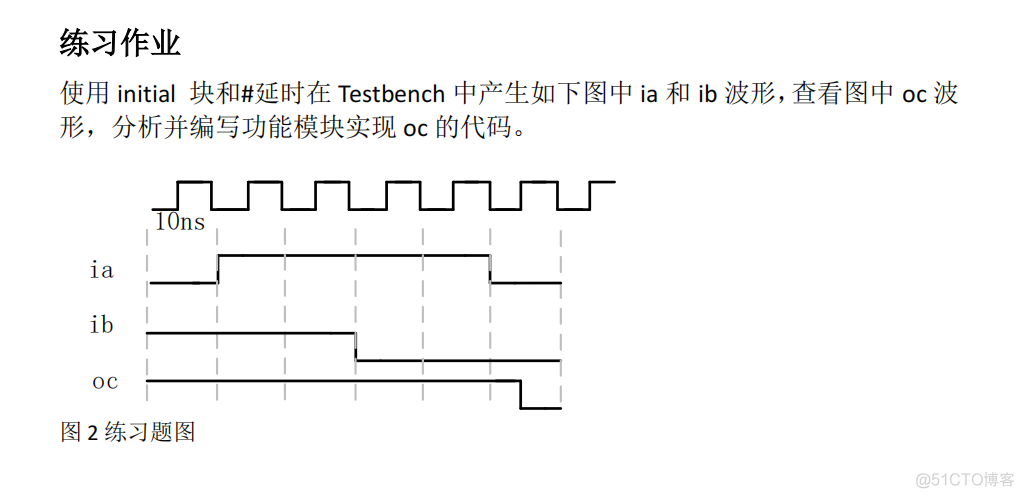

initial begin ia=0; #10 ia=1; #40 ia=0; end initial begin ib=1; #30 ib=0 end 这样也行 结果是一样的 两个initial块分开来 ia的时序就连起来了 ib的时序与其独立了 同一个initial块里写 ia,ib时序就得小心别弄错 是一个接一个的

oc有问题 波形一开始是红的 所以在功能模块里给oc赋初始值

但是这样好么?